### ANALOG DEVICES 24-Bit, 312 kSPS, 109 dB Sigma-Delta ADC with On-Chip Buffers and Serial Interface

### **Data Sheet**

### **FEATURES**

High performance 24-bit  $\Sigma$ - $\Delta$  ADC 115 dB dynamic range at 78.125 kHz output data rate 109 dB dynamic range at 312.5 kHz output data rate 312.5 kHz maximum fully filtered output word rate Pin-selectable oversampling rates of 64×, 128×, and 256× Low power mode Flexible serial peripheral interface (SPI) Fully differential modulator input On-chip differential amplifier for signal buffering **On-chip reference buffer** Full band, low-pass, finite impulse response (FIR) filter **Overrange alert pin Digital gain correction registers** Power-down mode Synchronization of multiple devices via the SYNC pin **Daisy chaining**

### **APPLICATIONS**

**Data acquisition systems Vibration analysis** Instrumentation

### **GENERAL DESCRIPTION**

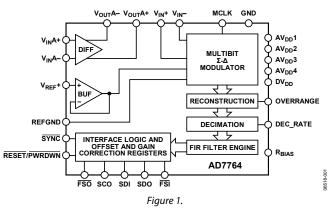

The AD7764 is a high performance, 24-bit, sigma-delta ( $\Sigma$ - $\Delta$ ) analog-to-digital converter (ADC). It combines wide input bandwidth, high speed, and performance of 109 dB dynamic range at a 312.5 kHz output data rate. With excellent dc specifications, the converter is ideal for high speed data acquisition of ac signals where dc data is also required.

Using the AD7764 eases front-end antialias filtering requirements, simplifying the design process significantly. The AD7764 offers pin-selectable decimation rates of 64×, 128×, and 256×. Other features include an integrated buffer to drive the reference, as well as a fully differential amplifier to buffer and level shift the input to the modulator.

An overrange alert pin indicates when an input signal exceeds the acceptable range. The addition of internal gain and internal overrange registers makes the AD7764 a compact, highly integrated data acquisition device requiring minimal peripheral components.

The AD7764 also offers a low power mode, significantly reducing power dissipation without reducing the output data rate or available input bandwidth.

### FUNCTIONAL BLOCK DIAGRAM

**AD7764**

#### Table 1. Related Devices

| Device No. | Description                                       |

|------------|---------------------------------------------------|

| AD7760     | 2.5 MSPS, 100 dB, parallel output, on-chip buffer |

| AD7762     | 625 kSPS, 109 dB, parallel output, on-chip buffer |

| AD7763     | 625 kSPS, 109 dB, serial output, on-chip buffers  |

| AD7765     | 156 kSPS, 112 dB, serial output, on-chip buffers  |

| AD7766     | 128 kSPS/64 kSPS/32 kSPS, 8.5 mW, 109 dB SNR      |

| AD7767     | 128 kSPS/64 kSPS/32 kSPS, 8.5 mW, 109 dB SNR      |

The differential input is sampled at up to 40 MSPS by an analog modulator. The modulator output is processed by a series of low-pass filters. The external clock frequency applied to the AD7764 determines the sample rate, filter corner frequencies, and output word rate.

The AD7764 device boasts a full band, on-board FIR filter. The full stop-band attenuation of the filter is achieved at the Nyquist frequency. This feature offers increased protection from signals that lie above the Nyquist frequency being aliased back into the input signal bandwidth.

The reference voltage supplied to the AD7764 determines the input range. With a 4 V reference, the analog input range is ±3.2768 V differential, biased around a common mode of 2.048 V. This common-mode biasing is achieved using the on-chip differential amplifier, further reducing the external signal conditioning requirements.

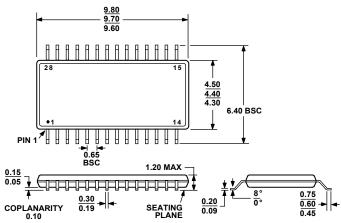

The AD7764 is available in a 28-lead TSSOP package and is specified over the industrial temperature range of -40°C to +85°C.

Rev. C

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2007–2018 Analog Devices, Inc. All rights reserved. **Technical Support** www.analog.com

# TABLE OF CONTENTS

| Features                                      |

|-----------------------------------------------|

| Applications1                                 |

| General Description                           |

| Revision History 2                            |

| Specifications                                |

| Timing Specifications7                        |

| Absolute Maximum Ratings                      |

| ESD Caution9                                  |

| Pin Configuration and Function Descriptions10 |

| Typical Performance Characteristics12         |

| Terminology16                                 |

| Theory of Operation17                         |

| Σ-Δ Modulation and Digital Filtering17        |

| AD7764 Antialias Protection20                 |

| Input Structure                               |

| On-Chip Differential Amplifier22              |

| Modulator Input Structure23                   |

| Driving the Modulator Inputs Directly 23      |

| AD7764 Serial Interface24                     |

| Reading Data24                                |

| Reading Status and Other Registers24          |

| Writing to the AD776424                       |

| Functionality                                 |

### **REVISION HISTORY**

| 1/2018—Rev. B to Rev. C                             |

|-----------------------------------------------------|

| Change to On-Chip Differential Amplifier Section 22 |

### 3/2017—Rev. A to Rev. B

| Changes to Features Section and General Description Section             | 1  |

|-------------------------------------------------------------------------|----|

| Changes to Table 2                                                      | 3  |

| Changes to Table 3                                                      | 6  |

| Change to Figure 3 Caption and Figure 4 Caption                         | 7  |

| Changes to Table 4                                                      | 8  |

| Changes to Table 5                                                      | 9  |

| Added Figure 29; Renumbered Sequentially                                | 14 |

| Changes to Terminology Section                                          | 15 |

| Changes to $\Sigma$ - $\Delta$ Modulation and Digital Filtering Section |    |

| and Table 6                                                             | 16 |

| Added Figure 34                                                         | 17 |

|                                                                         |    |

| Synchronization                   |

|-----------------------------------|

| Overrange Alerts                  |

| Power Modes                       |

| Decimation Rate Pin               |

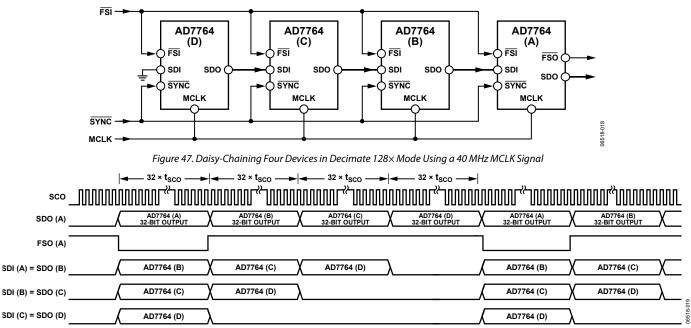

| Daisy-Chaining2                   |

| Reading Data in Daisy-Chain Mode  |

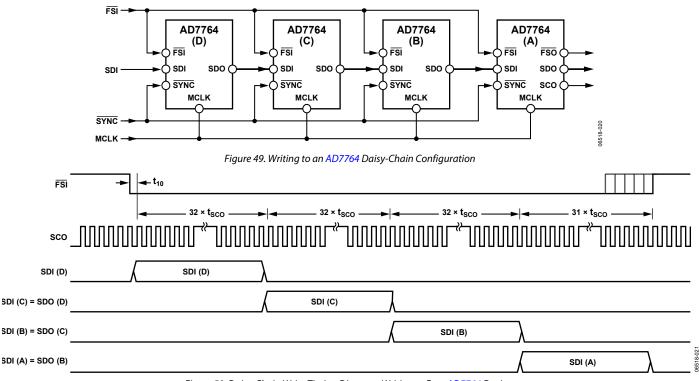

| Writing Data in Daisy-Chain Mode  |

| Clocking the AD7764               |

| MCLK Jitter Requirements          |

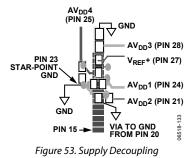

| Decoupling and Layout Information |

| Supply Decoupling                 |

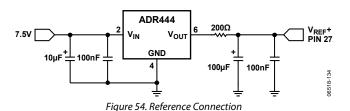

| Reference Voltage Filtering       |

| Differential Amplifier Components |

| Layout Considerations             |

| Using the AD7764                  |

| Bias Resistor Selection           |

| AD7764 Registers                  |

| Control Register                  |

| Status Register                   |

| Gain Register—Address 0x0004      |

| Overrange Register—Address 0x0005 |

| Outline Dimensions                |

| Ordering Guide                    |

| Change to Table 7                                        | 17    |

|----------------------------------------------------------|-------|

| Added Table 8 and Table 9                                | 18    |

| Changes to On-Chip Differential Amplifier Section        |       |

| and Table 10                                             | 21    |

| Changes to AD7764 Serial Interface Section Title and Re- | ading |

| Data Section                                             | 23    |

| Changes to Functionality Section Title                   | 24    |

| Changes to Table 14                                      | 25    |

| Changes to Table 15                                      | 26    |

| Changes to Table 17, Table 18, and Table 19              | 31    |

|                                                          |       |

### 11/2009—Rev. 0 to Rev. A

| Changes to Table 2                                                      | 4  |

|-------------------------------------------------------------------------|----|

| Changes to Table 3                                                      | 6  |

| Changes to Table 4                                                      | 8  |

| Changes to Typical Performance Characteristics Section,                 |    |

| Introductory Text                                                       | 11 |

| Changes to $\Sigma$ - $\Delta$ Modulation and Digital Filtering Section | 16 |

| Added AD7764 Antialias Protection Section                               | 17 |

| Changes to Figure 35                                                    | 19 |

|                                                                         |    |

| Added Driving the Modulator Inputs Directly Section, Includin | ng  |

|---------------------------------------------------------------|-----|

| Figure 39 and Figure 40, Renumbered Subsequent Figures        | .20 |

| Changes to Synchronization Section, Added Figure 41           | .22 |

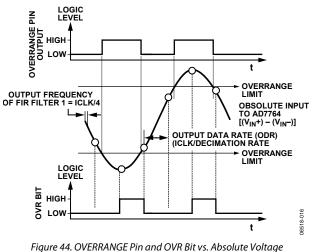

| Changes to Power Modes Section, Added Figure 44               | .23 |

| Changes to Example 2 Section                                  | .26 |

| Changes to Using the AD7764 Section                           | .28 |

|                                                               |     |

6/2007—Revision 0: Initial Version

# **SPECIFICATIONS**

$AV_{DD}1 = DV_{DD} = 2.5 \text{ V}, AV_{DD}2 = AV_{DD}3 = AV_{DD}4 = 5 \text{ V}, V_{REF} + = 4.096 \text{ V}, MCLK amplitude = 5 \text{ V}, T_A = 25^{\circ}\text{C}$ , normal power mode, using the on-chip amplifier with components, as shown in the Optimal row in Table 10, unless otherwise noted.<sup>1</sup>

| Parameter                                | Test Conditions/Comments                                                                                                      | Min | Тур   | Max  | Unit |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|------|

| DYNAMIC PERFORMANCE                      |                                                                                                                               |     |       |      |      |

| Decimate 256×                            |                                                                                                                               |     |       |      |      |

| Normal Power Mode                        | MCLK = 40 MHz, output data rate (ODR) = 78.125 kHz, $f_{IN}$ = 1 kHz sine wave                                                |     |       |      |      |

| Dynamic Range                            | Modulator inputs shorted                                                                                                      | 110 | 115   |      | dB   |

|                                          | Differential amplifier inputs shorted                                                                                         |     | 113.4 |      | dB   |

| Signal-to-Noise Ratio (SNR) <sup>2</sup> | Input amplitude = -0.5 dB                                                                                                     | 106 | 109   |      | dB   |

| Spurious-Free Dynamic Range<br>(SFDR)    | Nonharmonic                                                                                                                   |     | 130   |      | dBFS |

| Total Harmonic Distortion (THD)          | Input amplitude = $-0.5 \text{ dB}$                                                                                           |     | -105  |      | dB   |

|                                          | Input amplitude = –6 dB                                                                                                       |     | -103  |      | dB   |

|                                          | Input amplitude = -60 dB                                                                                                      |     | -71   |      | dB   |

| Low Power Mode                           | $\label{eq:MCLK} \begin{split} MCLK = & 40 \; MHz, \; ODR = & 78.125 \; kHz, \; f_{IN} = & 1 \; kHz \\ sine wave \end{split}$ |     |       |      |      |

| Dynamic Range                            | Modulator inputs shorted                                                                                                      | 110 | 113   |      | dB   |

|                                          | Differential amplifier inputs shorted                                                                                         |     | 112   |      | dB   |

| SNR <sup>2</sup>                         | Input amplitude = -0.5 dB                                                                                                     | 106 | 109   |      | dB   |

| THD                                      | Input amplitude = -0.5 dB                                                                                                     |     | -105  |      | dB   |

|                                          | Input amplitude = –6 dB                                                                                                       |     | -111  | -100 | dB   |

|                                          | Input amplitude = –60 dB                                                                                                      |     | -76   |      | dB   |

| Decimate 128×                            |                                                                                                                               |     |       |      |      |

| Normal Power Mode                        | MCLK = 40 MHz, ODR = 156.25 kHz, $f_{IN}$ = 1 kHz sine wave                                                                   |     |       |      |      |

| Dynamic Range                            | Modulator inputs shorted                                                                                                      | 108 | 112   |      | dB   |

|                                          | Differential amplifier inputs shorted                                                                                         |     | 110.4 |      | dB   |

| SNR <sup>2</sup>                         |                                                                                                                               | 105 | 107   |      | dB   |

| SFDR                                     | Nonharmonic                                                                                                                   |     | 130   |      | dBFS |

| THD                                      | Input amplitude = -0.5 dB                                                                                                     |     | -105  |      | dB   |

|                                          | Input amplitude = –6 dB                                                                                                       |     | -103  |      | dB   |

| Intermodulation Distortion (IMD)         | Input amplitude = $-6 \text{ dB}$ , $f_{IN} A = 50.3 \text{ kHz}$ , $f_{IN} B = 47.3 \text{ kHz}$                             |     |       |      |      |

|                                          | Second-order terms                                                                                                            |     | -117  |      | dB   |

|                                          | Third-order terms                                                                                                             |     | -108  |      | dB   |

| Low Power Mode                           | MCLK = 40 MHz, ODR = 156.25 kHz, $f_{IN}$ = 1 kHz sine wave                                                                   |     |       |      |      |

| Dynamic Range                            | Modulator inputs shorted                                                                                                      | 109 | 110   |      | dB   |

|                                          | Differential amplifier inputs shorted                                                                                         |     | 109   |      | dB   |

| SNR <sup>2</sup>                         | Input amplitude = -0.5 dB                                                                                                     | 105 | 107   |      | dB   |

| THD                                      | Input amplitude = -0.5 dB                                                                                                     |     | -105  |      | dB   |

|                                          | Input amplitude = -6 dB                                                                                                       |     | -111  |      | dB   |

|                                          | Input amplitude = –6 dB                                                                                                       |     |       | -100 | dB   |

| IMD                                      | Input amplitude = $-6 \text{ dB}$ , $f_{IN} \text{ A} = 50.3 \text{ kHz}$ , $f_{IN} \text{ B} = 47.3 \text{ kHz}$             |     |       |      |      |

|                                          | Second-order terms                                                                                                            |     | -134  |      | dB   |

|                                          | Third-order terms                                                                                                             |     | -110  |      | dB   |

# **Data Sheet**

| Parameter                                  | Test Conditions/Comments                                                                           | Min   | Тур     | Max              | Unit             |

|--------------------------------------------|----------------------------------------------------------------------------------------------------|-------|---------|------------------|------------------|

| Decimate 64×                               |                                                                                                    |       |         |                  |                  |

| Normal Power Mode                          | MCLK = 40 MHz, ODR = 312.5 kHz, $f_{IN}$ = 1 kHz sine wave                                         |       |         |                  |                  |

| Dynamic Range                              | Modulator inputs shorted                                                                           | 105   | 109     |                  | dB               |

|                                            | Differential amplifier inputs shorted                                                              |       | 107.3   |                  | dB               |

| SNR <sup>2</sup>                           |                                                                                                    | 102.7 | 104     |                  | dB               |

| SFDR                                       | Nonharmonic                                                                                        |       | 130     |                  | dBFS             |

| Total Harmonic Distortion (THD)            | Input amplitude = –0.5 dB                                                                          |       | -105    |                  | dB               |

|                                            | Input amplitude = –6 dB                                                                            |       | -103    |                  | dB               |

| IMD                                        | Input amplitude = $-6 \text{ dB}$ , $f_{IN} A = 100.3 \text{ kHz}$ , $f_{IN} B = 97.3 \text{ kHz}$ |       |         |                  |                  |

|                                            | Second-order terms                                                                                 |       |         | -118             | dB               |

|                                            | Third-order terms                                                                                  |       |         | -108             | dB               |

| Low Power Mode                             |                                                                                                    |       |         |                  |                  |

| Dynamic Range                              | Modulator inputs shorted                                                                           | 105   | 106     |                  | dB               |

|                                            | Differential amplifier inputs shorted                                                              |       |         | 105.3            | dB               |

| SNR <sup>2</sup>                           | Input amplitude = -0.5 dB                                                                          | 4.00  | 103     |                  | dB               |

|                                            |                                                                                                    | 102   |         |                  | dB               |

| SFDR                                       | Nonharmonic                                                                                        |       | 110     |                  | dBFS             |

| THD                                        | Input amplitude = $-0.5 \text{ dB}$                                                                |       | -105    | 100              | dB               |

|                                            | Input amplitude = –6 dB                                                                            |       | -111    | -100             | dB               |

| DC ACCURACY<br>Resolution                  | Guaranteed monotonic to 24 bits                                                                    |       |         | 24               | Dita             |

|                                            | Normal power mode                                                                                  |       | 0.0036  | 24               | Bits<br>%        |

| Integral Nonlinearity                      | Low power mode                                                                                     |       | 0.0036  |                  | %                |

| Zero Error                                 | Normal power mode                                                                                  |       | 0.0014  | 0.03             | %                |

| Zelo Elloi                                 | Including on-chip amplifier                                                                        |       | 0.000   | 0.05             | %                |

|                                            | Low power mode                                                                                     |       | 0.04    | 0.024            | %                |

| Gain Error                                 | Low power mode                                                                                     |       | 0.002   | 0.024            | %                |

| Guillenoi                                  | Including on-chip amplifier                                                                        |       | 0.010   |                  | %                |

| Zero Error Drift                           | Does not include on-chip amplifier                                                                 |       | 0.00006 |                  | %FS/°C           |

| Gain Error Drift                           | Does not include on-chip amplifier                                                                 |       | 0.00005 |                  | %FS/°C           |

| DIGITAL FILTER CHARACTERISTICS             | Normal and low power modes                                                                         |       | 0.00005 |                  | 701 <b>3</b> 7 C |

| Pass-Band Ripple                           | Normal and low power modes                                                                         |       | 0.1     |                  | dB               |

| Pass Band <sup>3</sup>                     | –1 dB frequency                                                                                    |       |         | ODR×<br>0.4016   | kHz              |

| -3 dB Bandwidth <sup>3</sup>               |                                                                                                    |       |         | ODR ×<br>0.4096  | kHz              |

| Stop Band <sup>3</sup>                     | Beginning of stop band                                                                             |       |         | $ODR \times 0.5$ | kHz              |

| Stop-Band Attenuation                      | Decimate 64× and decimate 128× modes                                                               |       | -120    |                  | dB               |

|                                            | Decimate 256×                                                                                      |       | -115    |                  | dB               |

| Group Delay                                | See Table 8 and Table 9                                                                            |       |         |                  | 1                |

| ANALOG INPUT                               |                                                                                                    |       |         |                  |                  |

| Differential Input Voltage                 | Modulator input pins: $V_{IN}$ + - $V_{IN}$ -, $V_{REF}$ + = 4.096 V                               |       |         | ±3.2768          | V р-р            |

| Input Capacitance                          | At on-chip differential amplifier inputs                                                           |       | 5       |                  | pF               |

|                                            | At modulator inputs                                                                                |       | 29      |                  | pF               |

| REFERENCE INPUT/OUTPUT                     |                                                                                                    |       |         |                  |                  |

| V <sub>REF+</sub> Input Voltage            | $AV_{DD}3 = 5 V \pm 5\%$                                                                           |       |         | 4.096            | V                |

| V <sub>REF+</sub> Input DC Leakage Current |                                                                                                    |       |         | ±1               | μΑ               |

| V <sub>REF+</sub> Input Capacitance        |                                                                                                    |       | 5       |                  | pF               |

| Parameter                                          | Test Conditions/Comments                                                         | Min   | Тур   | Max                  | Unit   |

|----------------------------------------------------|----------------------------------------------------------------------------------|-------|-------|----------------------|--------|

| DIGITAL INPUT/OUTPUT                               |                                                                                  |       |       |                      |        |

| MCLK Input Amplitude                               |                                                                                  | 2.25  |       | 5.25                 | V      |

| Input Capacitance                                  |                                                                                  |       | 7.3   |                      | рF     |

| Input Leakage Current                              |                                                                                  |       |       | ±1                   | µA/pin |

| VINH                                               |                                                                                  | 0.8×  |       |                      | V      |

|                                                    |                                                                                  | DVDD  |       |                      |        |

| VINL                                               |                                                                                  |       |       | $0.2 \times DV_{DD}$ | V      |

| V <sub>OH</sub> <sup>4</sup>                       |                                                                                  | 2.2   |       |                      | V      |

| Vol                                                |                                                                                  |       |       | 0.1                  | V      |

| ON-CHIP DIFFERENTIAL AMPLIFIER                     |                                                                                  |       |       |                      |        |

| Input Impedance                                    |                                                                                  |       | >1    |                      | MΩ     |

| Bandwidth for 0.1 dB Flatness                      |                                                                                  |       |       | 125                  | kHz    |

| Common-Mode Input Voltage⁵                         | Common-mode voltage at amplifier input pins; $V_{IN}A+$ and $V_{IN}A-$           | 0.8   |       | 2.2                  | V      |

| Common-Mode Output Voltage                         | On-chip differential amplifier pins, V <sub>OUT</sub> A+ and V <sub>OUT</sub> A– |       | 2.048 |                      | V      |

| POWER REQUIREMENTS                                 |                                                                                  |       |       |                      |        |

| AV <sub>DD</sub> 1 (Modulator Supply)              |                                                                                  | 2.375 |       | 2.625                | V      |

| AV <sub>DD</sub> 2 (General Supply)                |                                                                                  | 4.75  |       | 5.25                 | V      |

| AV <sub>DD</sub> 3 (Differential Amplifier Supply) | 5 V supply required for 4.096 V reference                                        | 3.15  |       | 5.25                 | V      |

| AV <sub>DD</sub> 4 (Reference Buffer Supply)       | 5 V supply required for 4.096 V reference                                        | 3.15  |       | 5.25                 | V min/ |

|                                                    |                                                                                  |       |       |                      | max    |

| DV <sub>DD</sub>                                   | ±5%                                                                              | 2.375 |       | 2.625                | V      |

| Normal Power Mode                                  |                                                                                  |       |       |                      |        |

| Al <sub>DD</sub> 1 (Modulator)                     |                                                                                  |       | 19    |                      | mA     |

| Al <sub>DD</sub> 2 (General) <sup>6</sup>          | MCLK = 40 MHz                                                                    |       | 13    |                      | mA     |

| Al <sub>DD</sub> 3 (Differential Amplifier)        | $AV_{DD}3 = 5 V$                                                                 |       | 10    |                      | mA     |

| Al <sub>DD</sub> 4 (Reference Buffer)              | $AV_{DD}4 = 5 V$                                                                 |       | 9     |                      | mA     |

| DI <sub>DD</sub> <sup>6</sup>                      | MCLK = 40 MHz                                                                    |       | 37    |                      | mA     |

| Low Power Mode                                     |                                                                                  |       |       |                      |        |

| Al <sub>DD</sub> 1 (Modulator)                     |                                                                                  |       | 10    |                      | mA     |

| Al <sub>DD</sub> 2 (General) <sup>6</sup>          | MCLK = 40 MHz                                                                    |       | 7     |                      | mA     |

| Alddd (Differential Amplifier)                     | $AV_{DD}3 = 5 V$                                                                 |       | 5.5   |                      | mA     |

| Al <sub>DD</sub> 4 (Reference Buffer)              | $AV_{DD}4 = 5 V$                                                                 |       | 5     |                      | mA     |

| DI <sub>DD</sub> <sup>6</sup>                      | MCLK = 40 MHz                                                                    |       | 20    |                      | mA     |

| POWER DISSIPATION                                  |                                                                                  |       |       |                      |        |

| Normal Power Mode                                  | MCLK = 40 MHz, decimate $64 \times$                                              |       | 300   | 371                  | mW     |

| Low Power Mode                                     | MCLK = 40 MHz, decimate $64 \times$                                              |       | 160   | 215                  | mW     |

| Power-Down Mode <sup>7</sup>                       | PWRDWN pin held logic low                                                        |       | 1     |                      | mW     |

<sup>1</sup> See the Terminology section. <sup>2</sup> SNR specifications in decibels are referred to a full-scale input, FS, and are tested with an input signal at 0.5 dB below full scale, unless otherwise specified.

<sup>3</sup> The output data rate (ODR) = [(MCLK/2)]/decimation rate. That is, the maximum ODR for the AD7764 = [(40 MHz)/2)/64] = 312.5 kHz.

<sup>4</sup> Tested with a 400 µA load current. <sup>5</sup> Specified min and max values relate to the common mode voltage at which the protection circuitry on the pins (V<sub>N</sub>A+ and V<sub>N</sub>A−) starts to turn on. Prior to this turn on, the THD of the AD7764 degrades at common modes approaching 2 V, or on the lower side approaching 1 V. <sup>6</sup> Tested at MCLK = 40 MHz. This current scales linearly with the applied MCLK frequency.

<sup>7</sup> Tested at 125°C.

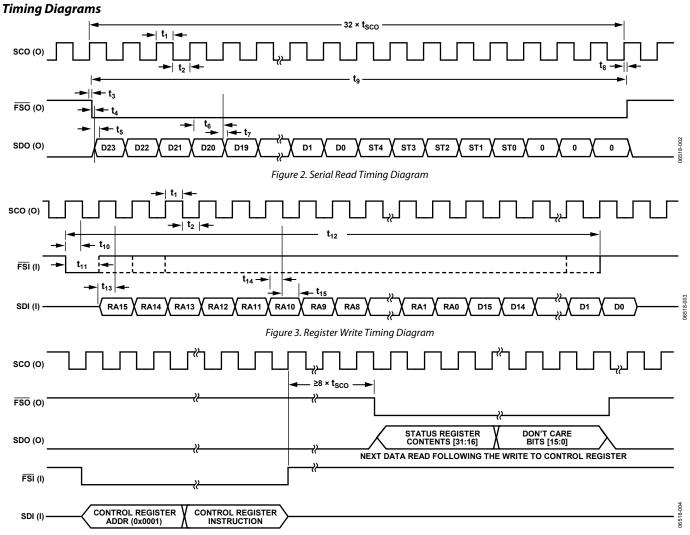

### TIMING SPECIFICATIONS

$AV_{\rm DD}1 = DV_{\rm DD} = 2.5 \text{ V}, \ AV_{\rm DD}2 = AV_{\rm DD}3 = AV_{\rm DD}4 = 5 \text{ V}, \ V_{\rm REF} + = 4.096 \text{ V}, \ T_{\rm A} = 25^{\circ}\text{C}, \ C_{\rm LOAD} = 25 \text{ pF}.$

| Table | . 3 |

|-------|-----|

| Lable | 23. |

|                              | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> |                     |                     |      |                                                                 |  |  |

|------------------------------|----------------------------------------------|---------------------|---------------------|------|-----------------------------------------------------------------|--|--|

| Parameter                    | Min                                          | Тур                 | Max                 | Unit | Description                                                     |  |  |

| f <sub>MCLK</sub>            | 500                                          |                     |                     | kHz  | Applied master clock frequency                                  |  |  |

|                              |                                              |                     | 40                  | MHz  |                                                                 |  |  |

| f <sub>ICLK</sub>            | 250                                          |                     |                     | kHz  | Internal modulator clock derived from MCLK                      |  |  |

|                              |                                              |                     | 20                  | MHz  |                                                                 |  |  |

| t1                           |                                              | $1 \times t_{ICLK}$ |                     | sec  | SCO high period                                                 |  |  |

| t <sub>2</sub>               |                                              | $1 \times t_{ICLK}$ |                     | sec  | SCO low period                                                  |  |  |

| t <sub>3</sub>               |                                              | 1                   | 2.5                 | ns   | SCO rising edge to FSO falling edge                             |  |  |

| t4                           |                                              | 2                   | 3.5                 | ns   | Data access time, FSO falling edge to data active               |  |  |

| t <sub>5</sub>               |                                              |                     | 8                   | ns   | MSB data access time, SDO active to SDO valid                   |  |  |

| t <sub>6</sub>               | 40                                           |                     |                     | ns   | Data hold time (SDO valid to SCO rising edge)                   |  |  |

| t7                           |                                              |                     | 9.5                 | ns   | Data access time (SCO rising edge to SDO valid)                 |  |  |

| t <sub>8</sub>               |                                              | 2                   | 2.5                 | ns   | SCO rising edge to FSO rising edge                              |  |  |

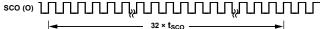

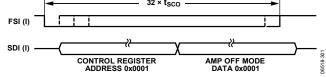

| t9                           |                                              |                     | $32 \times t_{sco}$ | sec  | FSO low period                                                  |  |  |

| t <sub>10</sub>              | 12                                           |                     |                     | ns   | Setup time from FSI falling edge to SCO falling edge            |  |  |

| t11                          | 1 × t <sub>sco</sub>                         |                     |                     | sec  | FSI low period                                                  |  |  |

| t <sub>12</sub> <sup>1</sup> |                                              |                     | $32 \times t_{sco}$ | sec  | FSI low period                                                  |  |  |

| t <sub>13</sub>              | 12                                           |                     |                     | ns   | SDI setup time for the first data bit                           |  |  |

| t <sub>14</sub>              | 12                                           |                     |                     | ns   | SDI setup time                                                  |  |  |

| t <sub>15</sub>              |                                              |                     | 0                   | ns   | SDI hold time                                                   |  |  |

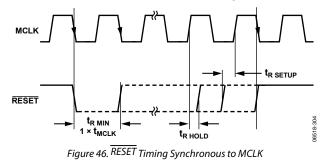

| t <sub>R MIN</sub>           | $1 	imes t_{MCLK}$                           |                     |                     | sec  | Minimum time for a valid RESET pulse                            |  |  |

| t <sub>R HOLD</sub>          | 5                                            |                     |                     | ns   | Minimum time between the MCLK rising edge and RESET rising edge |  |  |

| <b>t</b> r setup             | 5                                            |                     |                     | ns   | Minimum time between the RESET rising edge and MCLK rising edge |  |  |

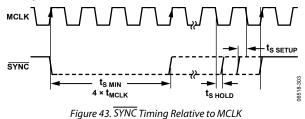

| t <sub>s MIN</sub>           | $4 \times t_{MCLK}$                          |                     |                     | sec  | Minimum time for a valid SYNC pulse                             |  |  |

| t <sub>s hold</sub>          | 5                                            |                     |                     | ns   | Minimum time between the MCLK falling edge and SYNC rising edge |  |  |

| ts setup                     | 5                                            |                     |                     | ns   | Minimum time between the SYNC rising edge and MCLK falling edge |  |  |

<sup>1</sup> This is the maximum time  $\overline{FSI}$  can be held low when writing to an individual device (a device that is not daisy-chained).

#### Figure 4. Status Register Read Cycle Timing Diagram

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 4.

| Parameter                                                            | Rating           |

|----------------------------------------------------------------------|------------------|

| AV <sub>DD</sub> 1 to Ground                                         | –0.3 V to +2.8 V |

| AV <sub>DD</sub> 2, AV <sub>DD</sub> 3, AV <sub>DD</sub> 4 to Ground | –0.3 V to +6 V   |

| DV <sub>DD</sub> to Ground                                           | –0.3 V to +2.8 V |

| V <sub>IN</sub> A+, V <sub>IN</sub> A– to Ground <sup>1</sup>        | –0.3 V to +6 V   |

| V <sub>IN</sub> +, V <sub>IN</sub> - to Ground <sup>1</sup>          | –0.3 V to +6 V   |

| Digital Input Voltage to Ground <sup>2</sup>                         | –0.3 V to +2.8 V |

| V <sub>REF</sub> + to Ground <sup>3</sup>                            | –0.3 V to +6 V   |

| AGND to DGND                                                         | –0.3 V to +0.3 V |

| Input Current to Any Pin Except Supplies <sup>4</sup>                | ±10 mA           |

| Operating Temperature Range, Commercial                              | –40°C to +85°C   |

| Storage Temperature Range                                            | –65°C to +150°C  |

| Junction Temperature                                                 | 150°C            |

| θ <sub>JA</sub> Thermal Impedance (1s0p) <sup>5</sup>                | 143°C/W          |

| $\theta_{JA}$ Thermal Impedance (2s2p) <sup>6, 7</sup>               | 71.1°C/W         |

| θ <sub>JC</sub> Thermal Impedance <sup>8</sup>                       | 20°C/W           |

| Solder Reflow Temperature <sup>9</sup>                               | 260°C            |

| ESD                                                                  | 1 kV             |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

$^1$  The absolute maximum voltage for  $V_{IN}-,\,V_{IN}+,\,V_{IN}A-,\,and\,V_{IN}A+$  is 6.0 V or  $AV_{DD}3+0.3$  V, whichever is lower.

$^2$  The absolute maximum voltage on the digital input is 3.0 V or  $DV_{\mbox{\tiny DD}}$  + 0.3 V, whichever is lower.

$^3$  The absolute maximum voltage on the  $V_{\text{REF}}+$  input is 6.0 V or  $AV_{\text{DD}}4+0.3$  V, whichever is lower.

<sup>4</sup> Transient currents of up to 100 mA do not cause SCR latch-up.

<sup>5</sup> 1s0p means a single-layer printed circuit board (PCB), which includes

one signal layer and zero power layers.

<sup>6</sup> 2s2p means a 4-layer PCB, which includes 2 signal layers and 2 power layers.

$^{7}$   $\theta_{JA}$  for a 2s2p PCB is derived from simulation.

$^{8}$  The revised  $\dot{\theta}_{JC}$  (thermal impedance) is derived from simulation.

<sup>9</sup> Maximum reflow temperature as per JEDEC J-SDT-020.

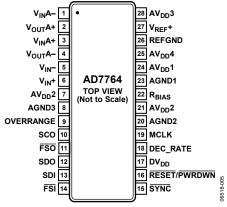

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 5. Pin Configuration

### Table 5. Pin Function Descriptions

|         | Mnemonic           |                                                                                                                                                                                                                                                                                       |

|---------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. |                    | Description                                                                                                                                                                                                                                                                           |

| 1       | V <sub>IN</sub> A- | Negative Input to the Differential Amplifier.                                                                                                                                                                                                                                         |

| 2       | VoutA+             | Positive Output from the Differential Amplifier.                                                                                                                                                                                                                                      |

| 3       | V <sub>IN</sub> A+ | Positive Input to the Differential Amplifier.                                                                                                                                                                                                                                         |

| 4       | VoutA-             | Negative Output from the Differential Amplifier.                                                                                                                                                                                                                                      |

| 5       | V <sub>IN</sub> -  | Negative Input to the Modulator.                                                                                                                                                                                                                                                      |

| 6       | V <sub>IN</sub> +  | Positive Input to the Modulator.                                                                                                                                                                                                                                                      |

| 7, 21   | AV <sub>DD</sub> 2 | 5 V Power Supply. Decouple Pin 7 to AGND3 (Pin 8) with a 100 nF capacitor. Decouple Pin 21 to AGND1 (Pin 23) with a 100 nF capacitor.                                                                                                                                                 |

| 8       | AGND3              | Power Supply Ground for the Analog Circuitry.                                                                                                                                                                                                                                         |

| 9       | OVERRANGE          | Overrange Pin. This pin outputs a logic high to indicate that the user applied an analog input that is approaching the limit of the analog input to the modulator.                                                                                                                    |

| 10      | SCO                | Serial Clock Out. This clock signal is derived from the internal ICLK signal. The frequency of this clock is equal to ICLK. See the Clocking the AD7764 section for more information.                                                                                                 |

| 11      | FSO                | Frame Sync Out. This signal frames the serial data output and is 32 SCO periods wide.                                                                                                                                                                                                 |

| 12      | SDO                | Serial Data Out. Data and status are output on this pin during each serial transfer. Each bit is clocked out on an SCO rising edge and is valid on the falling edge. See the AD7764 Serial Interface section for further details.                                                     |

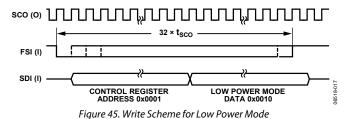

| 13      | SDI                | Serial Data In. The first data bit (MSB) must be valid on the next SCO falling edge after the FSI event is                                                                                                                                                                            |

|         |                    | latched. Thirty-two bits are required for each write; the first 16-bit word contains the device and register address, and the second word contains the data. See the AD7764 Serial Interface section for more information.                                                            |

| 14      | FSI                | Frame Sync Input. The status of this pin is checked on the falling edge of SCO. If this pin is low, then the first data bit is latched in on the next SCO falling edge. See the AD7764 Serial Interface section for more information.                                                 |

| 15      | SYNC               | Synchronization Input. A falling edge on this pin resets the internal filter. Use this pin to synchronize multiple devices in a system. See the Synchronization section for more information.                                                                                         |

| 16      | RESET/PWRDWN       | Reset/Power-Down Pin. When a logic low is sensed on this pin, the device is powered down and all internal circuitry is reset.                                                                                                                                                         |

| 17      |                    | 2.5 V Power Supply for the Digital Circuitry and FIR Filter. Decouple this pin to the ground plane with a 100 nF capacitor.                                                                                                                                                           |

| 18      | DEC_RATE           | Decimation Rate Pin. This pin selects one of the three decimation rate modes. When 2.5 V is applied to this pin, a decimation rate of 64× is selected. Select a decimation rate of 128× by leaving this pin floating. Select a decimation rate of 256× by setting this pin to ground. |

| 19      | MCLK               | Master Clock Input. A low jitter digital clock must be applied to this pin. The output data rate depends on the frequency of this clock. See the Clocking the AD7764 section for more information.                                                                                    |

| 20      | AGND2              | Power Supply Ground for the Analog Circuitry.                                                                                                                                                                                                                                         |

| 22      | Rbias              | Bias Current Setting Pin. This pin must be decoupled to the ground plane. For more information, see the Bias Resistor Selection section.                                                                                                                                              |

# **Data Sheet**

\_\_\_\_

| Pin No. | Mnemonic           | Description                                                                                                              |

|---------|--------------------|--------------------------------------------------------------------------------------------------------------------------|

| 23      | AGND1              | Power Supply Ground for the Analog Circuitry.                                                                            |

| 24      | AV <sub>DD</sub> 1 | 2.5 V Power Supply for the Modulator. Decouple this pin to AGND1 (Pin 23) with a 100 nF capacitor.                       |

| 25      | AV <sub>DD</sub> 4 | 3.3 V to 5 V Power Supply for the Reference Buffer. Decouple this pin to AGND1 (Pin 23) with a 100 nF capacitor.         |

| 26      | REFGND             | Reference Ground. This pin is the ground connection for the reference voltage.                                           |

| 27      | V <sub>REF</sub> + | Reference Input.                                                                                                         |

| 28      | AV <sub>DD</sub> 3 | 3.3 V to 5 V Power Supply for the Differential Amplifier. Decouple this pin to the ground plane with a 100 nF capacitor. |

06518-212

06518-211

06518-210

150k

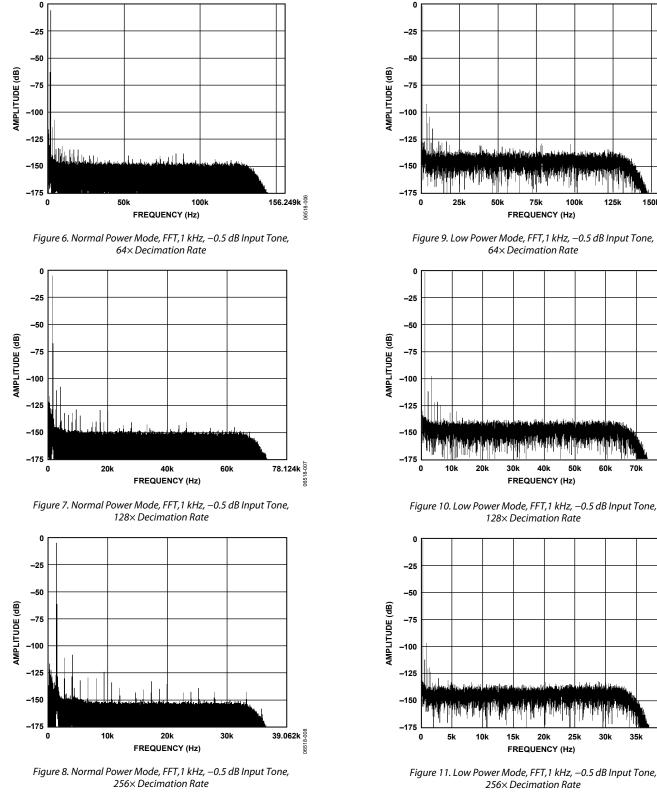

# **TYPICAL PERFORMANCE CHARACTERISTICS**

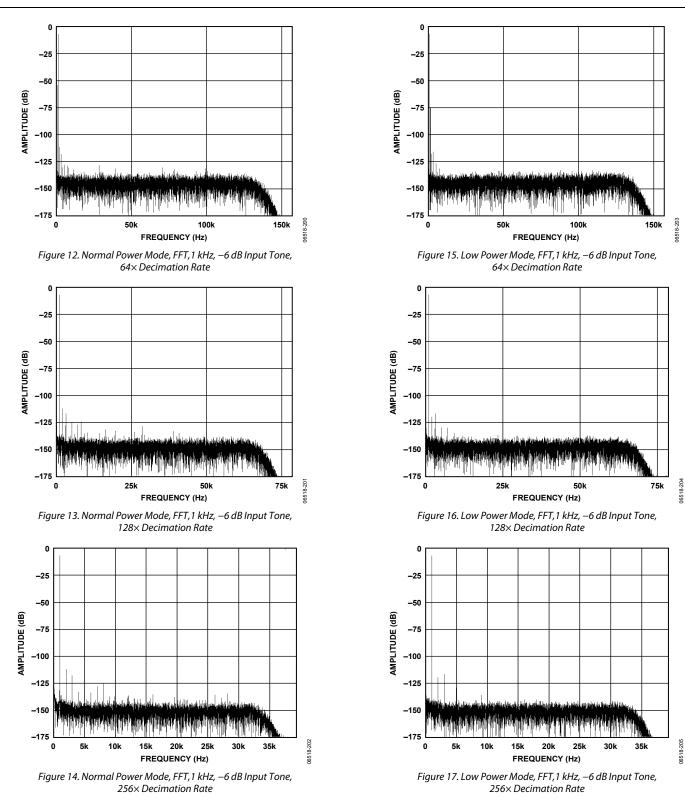

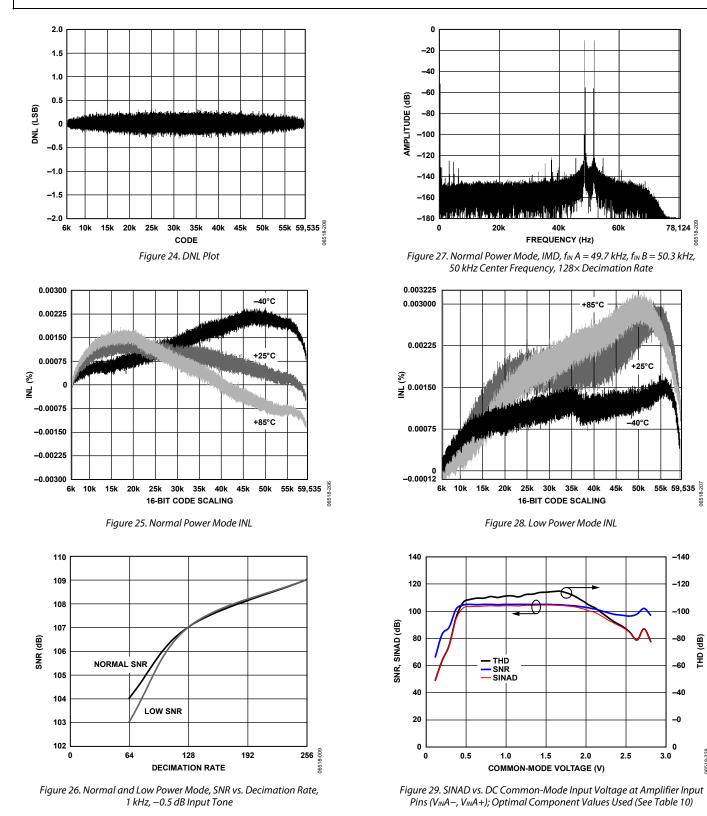

$AV_{DD}1 = DV_{DD} = 2.5 V$ ,  $AV_{DD}2 = AV_{DD}3 = AV_{DD}4 = 5 V$ ,  $V_{REF} + = 4.096 V$ , MCLK amplitude = 5 V,  $T_A = 25^{\circ}C$ . Linearity plots measured to 16-bit accuracy. Input signal reduced to avoid modulator overload and digital clipping; fast Fourier transforms (FFTs) of -0.5 dB tones are generated from 262,144 samples in normal power mode. All other FFTs are generated from 8192 samples.

### **Data Sheet**

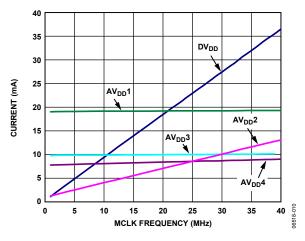

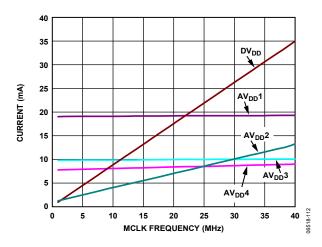

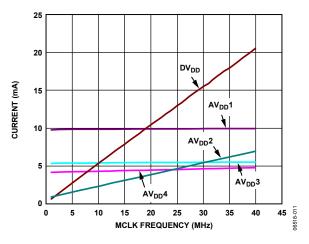

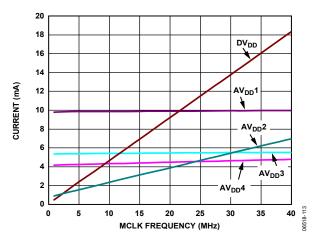

Figure 18. Normal Power Mode, Current Consumption vs. MCLK Frequency, 64× Decimation Rate

Figure 19. Normal Power Mode, Current Consumption vs. MCLK Frequency, 128× Decimation Rate

Figure 20. Normal Power Mode, Current Consumption vs. MCLK Frequency, 256× Decimation Rate

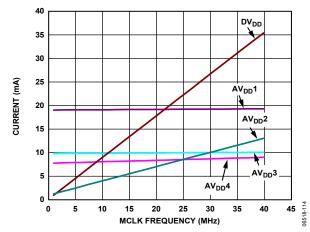

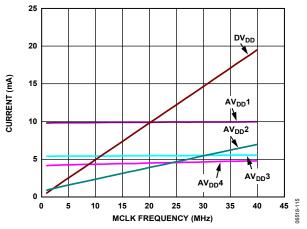

Figure 21. Low Power Mode, Current Consumption vs. MCLK Frequency, 64× Decimation Rate

Figure 22. Low Power Mode, Current Consumption vs. MCLK Frequency, 128× Decimation Rate

Figure 23. Low Power Mode, Current Consumption vs. MCLK Frequency, 256× Decimation Rate

### **Data Sheet**

AD7764

06518-329

### TERMINOLOGY

### Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below the Nyquist frequency, excluding harmonics and dc. The value for SNR is expressed in decibels (dB).

### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of the harmonics to the fundamental. For the AD7764, THD is defined as

$$THD(dB) = 20\log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

where:

$V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$ , and  $V_6$  are the rms amplitudes of the second to the sixth harmonics.

$V_l$  is the rms amplitude of the fundamental.

### Nonharmonic Spurious-Free Dynamic Range (SFDR)

Nonharmonic SFDR is the ratio of the rms signal amplitude to the rms value of the peak spurious spectral component, excluding harmonics.

### **Dynamic Range**

Dynamic range is the ratio of the rms value of the full scale to the rms noise measured with the inputs shorted together. The value for dynamic range is expressed in decibels.

### Intermodulation Distortion

With inputs consisting of sine waves at two frequencies, fa and fb, any active device with nonlinearities creates distortion products at sum and difference frequencies of mfa  $\pm$  nfb, where m, n = 0, 1, 2, 3, and so on. Intermodulation distortion terms are those for which neither m nor n is equal to 0. For example, the second-order terms include (fa + fb) and (fa - fb), while the third-order terms include (2fa + fb), (2fa - fb), (fa + 2fb), and (fa - 2fb).

The AD7764 is tested using the CCIF standard, where two input frequencies near the top end of the input bandwidth are used.

In this case, the second-order terms are typically distanced in frequency from the original sine waves, and the third-order terms are typically at a frequency close to the input frequencies. As a result, the second- and third-order terms are specified separately. The calculation of the intermodulation distortion is per the THD specification, where the calculation is the ratio of the rms sum of the individual distortion products to the rms amplitude of the sum of the fundamentals, expressed in decibels.

### Integral Nonlinearity (INL)

INL is the maximum deviation from a straight line passing through the endpoints of the ADC transfer function.

### Differential Nonlinearity (DNL)

DNL is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

### Zero Error

Zero error is the difference between the ideal midscale input voltage (when both inputs are shorted together) and the actual voltage producing the midscale output code.

### Zero Error Drift

Zero error drift is the change in the actual zero error value due to a temperature change of 1°C. It is expressed as a percentage of full scale at room temperature.

### **Gain Error**

The first code transition (from 100 ... 000 to 100 ... 001) occurs for an analog voltage 1/2 LSB above the nominal negative full scale. The last code transition (from 011 ... 110 to 011 ... 111) occurs for an analog voltage 1  $\frac{1}{2}$  LSB below the nominal full scale. The gain error is the deviation of the difference between the actual level of the last transition and the actual level of the first transition, from the difference between the ideal levels.

### **Gain Error Drift**

Gain error drift is the change in the actual gain error value due to a temperature change of 1°C. It is expressed as a percentage of full scale at room temperature.

# THEORY OF OPERATION

The AD7764 features an on-chip fully differential amplifier to feed the  $\Sigma$ - $\Delta$  modulator pins, an on-chip reference buffer, and a FIR filter block to perform the required digital filtering of the  $\Sigma$ - $\Delta$  modulator output. Using this  $\Sigma$ - $\Delta$  conversion technique with the added digital filtering, the analog input is converted to an equivalent digital word.

### $\Sigma\text{-}\Delta$ MODULATION AND DIGITAL FILTERING

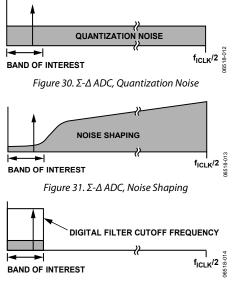

The input waveform applied to the modulator is sampled, and an equivalent digital word is output to the digital filter at a rate equal to  $f_{\rm ICLK}$ . By employing oversampling, the quantization noise is spread across a wide bandwidth from 0 to  $f_{\rm ICLK}$ . This means that the noise energy contained in the signal band of interest is reduced (see Figure 30). To further reduce the quantization noise, a high-order modulator is employed to shape the noise spectrum so that most of the noise energy is shifted out of the signal band (see Figure 31).

Figure 32.  $\Sigma$ - $\Delta$  ADC, Digital Filter Cutoff Frequency

The modulator sampling rate,  $f_{\rm ICLK}$ , is dependent on the power mode chosen. Table 6 details the relationship between MCLK and  $f_{\rm ICLK}$  across power mode. The AD7764 low power mode divides the MCLK by a factor of 4, reducing current consumption in both the analog and digital domains.

| Table 6. Modulator Sampling Rate vs. Power Mode |

|-------------------------------------------------|

|-------------------------------------------------|

| Power Mode | Modulator Sampling Rate (fICLK) |

|------------|---------------------------------|

| Normal     | MCLK/2                          |

| Low        | MCLK/4                          |

The digital filtering that follows the modulator removes the large out-of-band quantization noise (see Figure 32) while also reducing the data rate from  $f_{\rm ICLK}$  at the input of the filter to  $f_{\rm ICLK}$  /64 or less at the output of the filter, depending on the decimation rate used.

The AD7764 employs a sequence of three FIR filters in series to provide a digital filter with a low ripple pass band, a steep transition band, and excellent stop-band rejection, which starts at the Nyquist frequency. Achieving the stop-band rejection at the Nyquist frequency is beneficial because it prevents signals slightly greater than the Nyquist frequency, which are not protected by and external antialias filter from aliasing back in-band.

The AD7764 digital filter allows data to be output at three different output data rates (for any given MCLK input frequency) through setting the decimation ratio through the series of filters.

The first filter receives data from the modulator at  $f_{ICLK}$  MHz, where it is decimated 4× to the output data at ( $f_{ICLK}$ /4) MHz. The second filter allows the decimation rate to be chosen from 8× to 32×. The third filter has a fixed decimation rate of 2×.

Digital filters exhibit a group delay and settling time. The group delay of the filter is the delay from the change in analog input to when it is output by the digital filter. It is comprised of the computation plus the filter delays. The delay until valid data is available (when the FILTER\_SETTLE status bit is set) is approximately twice the filter delay plus the computation delay.

The group delay and settling time of a digital filter is apparent in the behavior of the ADC response to a SYNC input pulse.

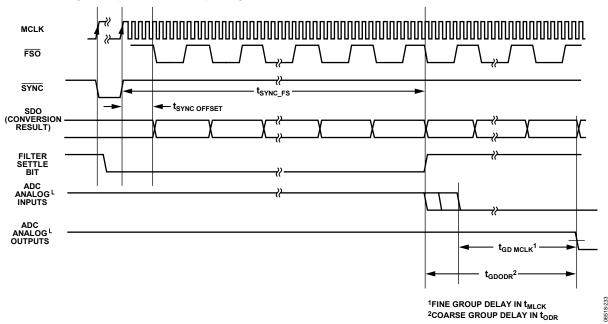

Table 8 and Table 9 describe the response of the AD7764 in both normal and low power modes to a SYNC pulse, in addition to providing the group delay and settling times. Figure 34 shows the effect of SYNC and the subsequent signals from the AD7764.

The SYNC rising edge sets a known point in time from which the digital filter begins to process inputs from the modulator. This is useful in building a simultaneous sampling solution with multiple AD7764 devices, all clocked by the same MCLK.

The logic level of the  $\overline{\text{SYNC}}$  pin is sampled by the rising edge of MCLK. Transitioning  $\overline{\text{SYNC}}$  from low to high on an MCLK falling edge is recommended. Following the rising edge of  $\overline{\text{SYNC}}$ , a number of MCLK periods pass before the first falling edge of  $\overline{\text{FSO}}$  indicates a conversion output; this number of MCLK periods is defined as  $t_{\text{SYNC}_OFFSET}$ . Beyond  $t_{\text{SYNC}_OFFSET}$ , a number of conversion periods, each indicated by the falling edge of  $\overline{\text{FSO}}$ , occur before the data from the filter is fully settled. During this time, outputs from the ADC have data that is a filtered mix of inputs to the modulator both before and after the time at which the  $\overline{\text{SYNC}}$  signal transitioned from logic low to logic high.

All outputs from the ADC exhibit a group delay. The constant delay, due to the digital filter, is described by the number of conversion periods  $(t_{ODR})$  that pass between a change occurring on the analog input being seen on the digital conversion output. Figure 34 illustrates the group delay, showing a scenario where there is a step change on the analog inputs after the filter initially settles. As shown, a given number of periods of the output data rate occur before the digital output shows the step change.

|                        | Group Delay (t <sub>GD_ODR</sub> ) in Output Data Rate<br>Periods |                |  |  |  |

|------------------------|-------------------------------------------------------------------|----------------|--|--|--|

| <b>Decimation Rate</b> | Normal Power Mode                                                 | Low Power Mode |  |  |  |

| 64×                    | 28                                                                | 29             |  |  |  |

| 128×                   | 28                                                                | 28             |  |  |  |

| 256×                   | 28                                                                | 28             |  |  |  |

| Table 7. Group Delay (tGD_ODR) Expressed in Periods of the | • |

|------------------------------------------------------------|---|

| Output Data Rate                                           |   |

Because the group delay is not an exact number of conversion periods, a more precise way to describe the term is in MCLK periods. The exact region within a given conversion period where the analog input change occurs determines which output data period the ADC output responds to with a change in the digital output. Figure 34 shows that, if the step change on the input occurs at later point in time within the output period, the digital output remains updated within the same ODR period.

Described as the fine group delay,  $t_{GDMCLK}$ , this delay consists of computation delay added to the actual delay through the filter provided in MCLK periods. Expressing the group delay in this manner allows it to be shown independent of the discrete steps of the ADC output data rate.

Figure 34. AD7764 Digital Filtering; Response to SYNC, Settling Time, and Group Delay

### Table 8. Filter Group Delay and Settling Time in Normal Power Mode

| Decimation<br>Rate | Filter<br>Computation<br>Delay (t <sub>MCLK</sub> ) | Filter<br>Delay<br>(t <sub>MCLK</sub> ) | t <sub>GDMCLK</sub><br>ADC<br>Group<br>Delay<br>(t <sub>MCLK</sub> ) | tsync_offset<br>(tmclk) | tsync_fs<br>SYNC to<br>FILTER_<br>SETTLE<br>Bit (tmclk) | Modulator<br>Sampling<br>Rate (f <sub>ICLK</sub> ) | Oversampling<br>Ratio (OSR) | Filter<br>Pass<br>Band | Output<br>Data Rate<br>(ODR) |

|--------------------|-----------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------|-------------------------|---------------------------------------------------------|----------------------------------------------------|-----------------------------|------------------------|------------------------------|

| 64×                | 80                                                  | 3504                                    | 3584                                                                 | 87                      | 7128                                                    | MCLK/2                                             | 64                          | ODR×<br>0.4            | MCLK/64                      |

| 128×               | 113                                                 | 6960                                    | 7073                                                                 | 141                     | 13,966                                                  | MCLK/2                                             | 128                         | ODR×<br>0.4            | MCLK/128                     |

| 256×               | 443                                                 | 13,608                                  | 14,051                                                               | 252                     | 27,901                                                  | MCLK/2                                             | 256                         | ODR×<br>0.4            | MCLK/256                     |

### Table 9. Filter Group Delay and Settling Time for Low Power Mode

| Decimation<br>Rate | Filter<br>Computation<br>Delay (t <sub>MCLK</sub> ) | Filter<br>Delay<br>(t <sub>MCLK</sub> ) | t <sub>GDMCLK</sub><br>ADC<br>Group<br>Delay<br>(t <sub>MCLK</sub> ) | tsync_offset<br>(tmclk) | SYNC to<br>FILTER_<br>SETTLE<br>Bit (t <sub>MCLK</sub> ) | Modulator<br>Sampling<br>Rate (f <sub>ICLK</sub> ) | Oversampling<br>Ratio (OSR) | Filter<br>Pass<br>Band | Output<br>Data Rate<br>(ODR) |

|--------------------|-----------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------|-------------------------|----------------------------------------------------------|----------------------------------------------------|-----------------------------|------------------------|------------------------------|

| 64×                | 120                                                 | 3552                                    | 3672                                                                 | 113                     | 7282                                                     | MCLK/4                                             | 32                          | ODR×<br>0.4            | MCLK/64                      |

| 128×               | 162                                                 | 7008                                    | 7170                                                                 | 167                     | 14,248                                                   | MCLK/4                                             | 64                          | ODR×<br>0.4            | MCLK/128                     |

| 256×               | 224                                                 | 13,920                                  | 14,144                                                               | 277                     | 27,926                                                   | MCLK/4                                             | 128                         | ODR×<br>0.4            | MCLK/256                     |

### **AD7764 ANTIALIAS PROTECTION**

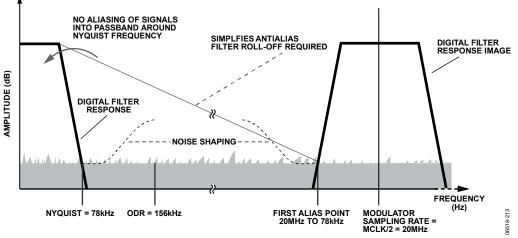

The decimation of the AD7764, along with its counterparts in the AD776x family, namely the AD7760, AD7762, AD7763, and AD7765, provides top of the range antialias protection.

The decimation filter of the AD7764 features more than 115 dB of attenuation across the full stop band, which ranges from the Nyquist frequency, namely ODR/2, up to  $I_{CLK} - ODR/2$  (where ODR is the output data rate). Starting the stop band at the Nyquist frequency prevents any signal component above Nyquist (and up to  $I_{CLK} - ODR/2$ ) from aliasing into the desired signal bandwidth.

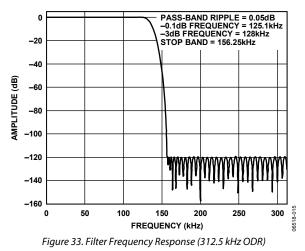

Figure 33 shows the frequency response of the decimation filter when the AD7764 is operated with a 40 MHz MCLK in decimate ×128 mode. Note that the first stop-band frequency occurs at Nyquist. The frequency response of the filter scales with both the decimation rate chosen and the MCLK frequency applied. When using low power mode, the modulator sample rate is MCLK/4.

Taking as an example the AD7764 in normal power and in decimate ×128 mode, the first possible alias frequency is at the ICLK frequency minus the pass band of the digital filter (see Figure 35).

Figure 35. Antialias Example Using the AD7764 in Normal Mode, Decimate ×128 Using MCLK/2 = ICLK = 20 MHz

### **INPUT STRUCTURE**

The AD7764 requires a 4.096 V input to the reference pin,  $V_{REF}$ , supplied by a high precision reference, such as the ADR444. Because the input to the  $\Sigma$ - $\Delta$  modulator of the device is fully differential, the effective differential reference range is 8.192 V.

$$V_{REF} + (Diff) = 2 \times 4.096 = 8.192 \text{ V}$$

As is inherent in  $\Sigma$ - $\Delta$  modulators, only a certain portion of this full reference can be used. With the AD7764, 80% of the full differential reference can be applied to the differential inputs of the modulator.

$Modulator\_Input_{FULL SCALE} = 8.192 \text{ V} \times 0.8 = 6.5536 \text{ V}$

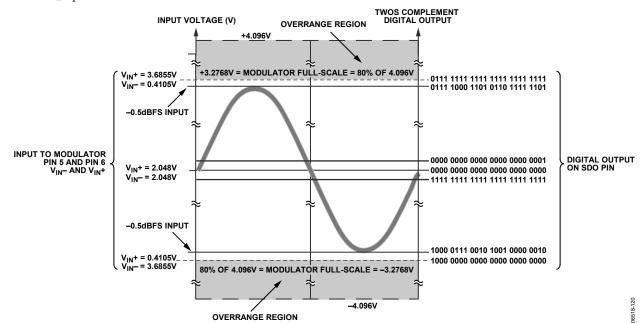

This means that a maximum of  $\pm 3.2768$  V p-p full scale can be applied to each of the AD7764 modulator inputs (Pin 5 and Pin 6), with the AD7764 being specified with an input -0.5 dB down from full scale (-0.5 dBFS). The AD7764 modulator inputs must have a common-mode input of 2.048 V.

Figure 36 shows the relative scaling between the differential voltages applied to the modulator pins and the respective 24-bit, twos complement digital outputs.

*Figure 36. AD7764 Scaling: Modulator Input Voltage vs. Digital Output Code*

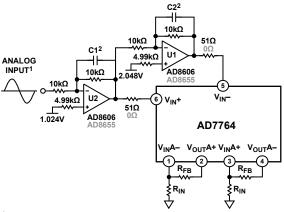

### **ON-CHIP DIFFERENTIAL AMPLIFIER**

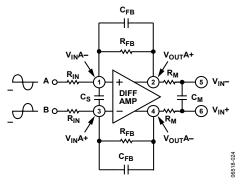

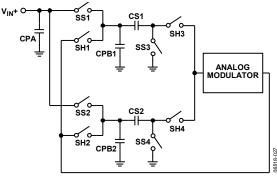

The AD7764 contains an on-board differential amplifier recommended to drive the modulator input pins. Pin 1, Pin 2, Pin 3, and Pin 4 on the AD7764 are the differential input and output pins of the amplifier. The external components,  $R_{IN}$ ,  $R_{FB}$ ,  $C_{FB}$ ,  $C_s$ , and  $R_M$ , are placed around Pin 1 through Pin 6 to create the recommended configuration.

To achieve the specified performance, configure the differential amplifier as a first-order antialias filter, as shown in Figure 37, using the component values listed in Table 10. The inputs to the differential amplifier are then routed through the external component network before being applied to the modulator inputs,  $V_{IN}$ - and  $V_{IN}$ + (Pin 5 and Pin 6). Using the optimal values in the table as an example yields a 25 dB attenuation at the first alias point of 19.6 MHz.

Figure 37. Differential Amplifier Configuration

| Table 10. On-Chip Differential Filter Component Values | Table 10. On-Chi | Differential Filter | Component Values |

|--------------------------------------------------------|------------------|---------------------|------------------|

|--------------------------------------------------------|------------------|---------------------|------------------|

| Value              | R <sub>IN</sub> | R <sub>FB</sub> | R <sub>M</sub> | Cs   | С <sub>ғв</sub> | С <sub>м</sub> |

|--------------------|-----------------|-----------------|----------------|------|-----------------|----------------|

|                    | (kΩ)            | (kΩ)            | (Ω)            | (pF) | (pF)            | (рF)           |

| Optimal            | 4.75            | 3.01            | 43             | 8.2  | 47              | 33             |

| Tolerance          | 2.37 to         | 2.4 to          | 36 to          | 0 to | 20 to           | 33 to          |

| Range <sup>1</sup> | 5.76            | 4.87            | 47             | 10   | 100             | 56             |

<sup>1</sup> The values shown are the acceptable tolerances for each component when altered relative to the optimal values that achieve the stated specifications of the device.

The range of values for each of the components in the differential amplifier configuration is listed in Table 10. When using the differential amplifier to gain the input voltages to the required modulator input range, it is recommended to implement the gain function by changing  $R_{\rm IN}$  and leaving  $R_{\rm FB}$  as the listed optimal value.

**Data Sheet**

The common-mode input at each of the differential amplifier input pins (V<sub>IN</sub>A+ and V<sub>IN</sub>A-) can range from 0.8 V dc to 2.2 V dc. The amplifier has a constant output common-mode voltage of 2.048 V, that is, V<sub>REF</sub>/2, the requisite common mode voltage for the modulator input pins (V<sub>IN</sub>+ and V<sub>IN</sub>-).

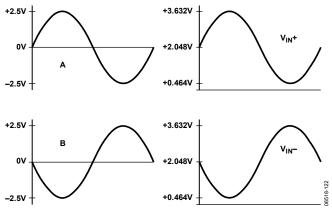

Figure 38 shows the signal conditioning that occurs using the differential amplifier configuration shown in Table 10 with a  $\pm 2.5$  V input signal to the differential amplifier. The amplifier in this example is biased around ground and is scaled to provide  $\pm 3.0935$  V p-p (-0.5 dBFS) on each modulator input with a 2.048 V common mode.

Figure 38. Differential Amplifier Signal Conditioning

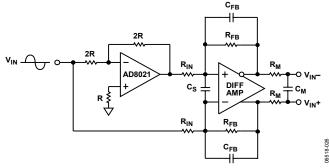

To obtain maximum performance from the AD7764, it is recommended to drive the ADC with differential signals. Figure 39 shows how a bipolar, single-ended signal biased around ground drives the AD7764 with the use of an external operational amplifier, such as the AD8021.

Figure 39. Single-Ended to Differential Conversion

### **MODULATOR INPUT STRUCTURE**